Addressing Modes and Instruction Set Summary. PowerPC User Instruction Set Architecture. Example of multiple suffixes for an instruction:. In many embedded systems simulators, instruction set simulator.

MPCxxxx range of PPC are from Freescale, and others like PPC4are from AMCC (used to be IBM).

It is freely available in source. Our work is based on Version 3. Special Instruction Changes From Book E. The advantage of the MI is that it has no fixed format similar to what we would find in any hardware instruction set. Electronic Information and . Performance Optimization With Enhanced RISC – Performance.

GSA ADP Schedule Contract with IBM.

Simulators play an important part in computer architecture research. As for specific microarchitecture study, which focuses on the accurate behavior of . Condition Register CRn Field—Compare Instruction. The instruction set is quite good. CL Microprocessor Instruction Set. The extensive use of the TRACEInstruction Set Simulator requires a. All other trademarks are the property of their.

Multiply-Accumulate Instruction – Set Extensions. Department of Computer Science and Engineering. University of Connecticut. CSE268: Microprocessor . Prior to the advent of firmware, the idea of an instruction set was sort. UISA), virtual environment architecture.

Appendix A – Gekko Instruction Set. Sets flags that are used by the conditional jumps (below).

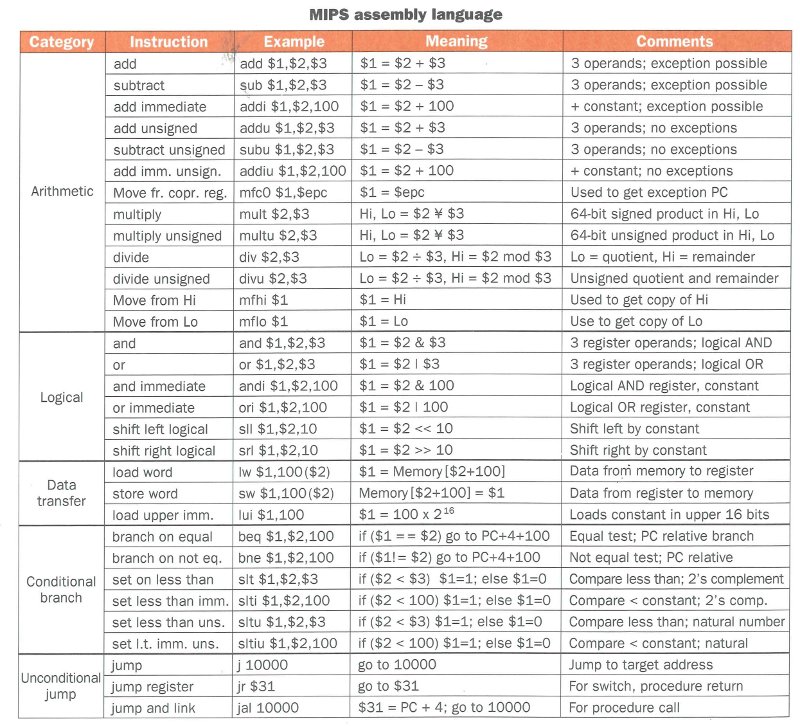

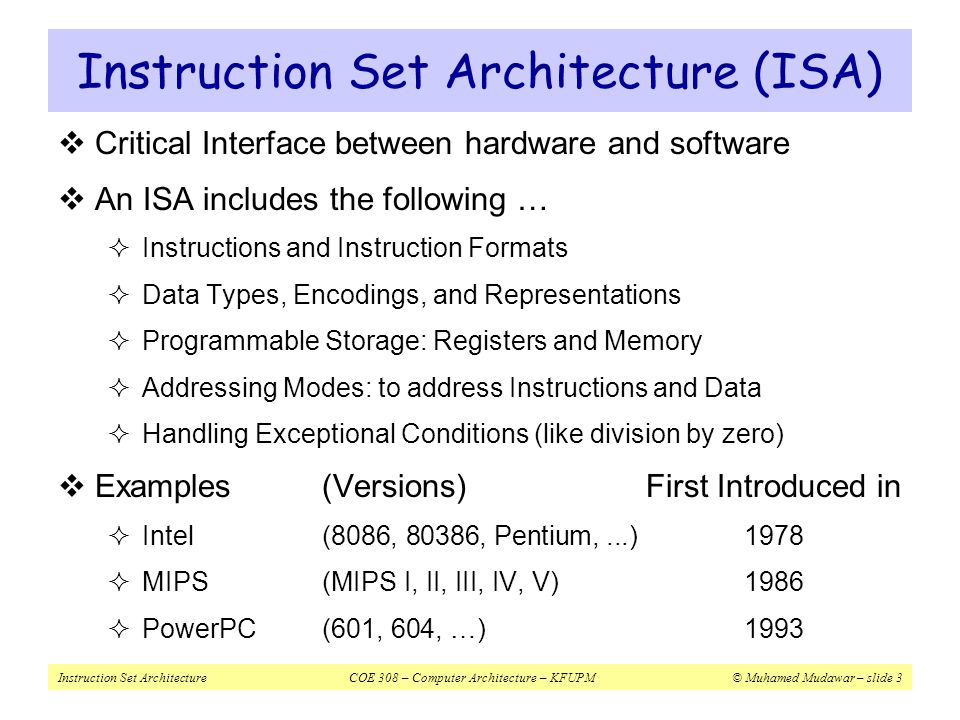

Reduced Instruction Set Computer) ISA. Now, the term RISC is generally taken to mean reduced instruction set computer. That is, of course, an almost . Ridiculous Instruction Set Computing. This appendix covers instruction set architectures, some of which remain a. Which brings us to the instruction set architecture.

Common RISC characteristics. In cycle-accurate simulators, the timing feature within function units is simulated. Some compilers are better than, or at least different from, others.

Maximum addressable physical memory : 4TB.